RISC : Comprendre le processeur à jeu d’instructions réduit

Aujourd’hui, on va voir en détail ce qu’est un processeur RISC, une architecture qui a profondément marqué l’évolution des systèmes embarqués et ordinateurs modernes. Le sigle RISC signifie « Reduced Instruction Set Computer », soit « ordinateur à jeu d’instructions réduit ». Cette approche se distingue par la simplicité et l’efficacité de son jeu d’instructions, optimisant la rapidité d’exécution et la consommation énergétique.

Principes fondamentaux du RISC

La philosophie RISC repose sur plusieurs idées clés :

- Instructions simples et uniformes : Les instructions RISC sont généralement de taille fixe et s’exécutent en un seul cycle d’horloge, contrairement aux architectures CISC (Complex Instruction Set Computer) qui proposent des instructions plus complexes et longues.

- Pipeline optimisé : La simplicité des instructions permet un traitement pipeline efficace, augmentant considérablement le débit d’instructions.

- Utilisation intensive des registres : Le processeur RISC possède un grand nombre de registres, ce qui limite les accès mémoire souvent plus lents.

- Chargement/Stockage : Les opérations arithmétiques et logiques ne s’effectuent qu’entre registres. L’accès à la mémoire se fait uniquement via des instructions dédiées de chargement ou de stockage.

Avantages et inconvénients

- Avantages :

- Exécution rapide des instructions, idéale pour le pipeline.

- Meilleure prévisibilité du temps d’exécution, facilitant la conception temps réel.

- Consommation énergétique réduite, adaptée aux systèmes embarqués.

- Architecture plus facile à concevoir et à optimiser.

- Inconvénients :

- Programme plus long, car certaines opérations complexes doivent être décomposées en plusieurs instructions simples.

- Plus grande taille de code mémoire, ce qui peut être un frein dans des environnements contraints.

Exemple simple d’instruction RISC vs CISC

Dans un processeur CISC, une instruction peut faire une opération complète comme additionner une valeur en mémoire directement à un registre. En RISC, cela nécessite plusieurs instructions :

- Charger la valeur mémoire dans un registre (LOAD).

- Ajouter cette valeur au registre cible (ADD).

- Stocker le résultat en mémoire si besoin (STORE).

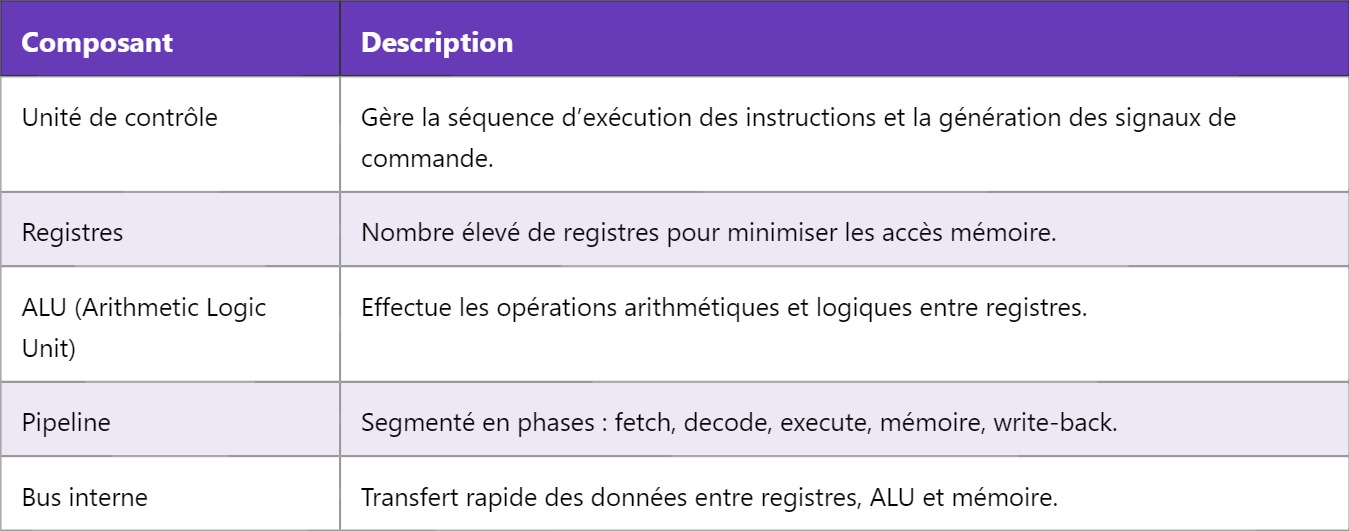

Structure typique d’un processeur RISC

Cas d’usage et impact dans l’industrie

Le modèle RISC a révolutionné la micro-informatique. Des architectures célèbres comme ARM, MIPS ou RISC-V sont basées sur ce concept. ARM domine aujourd’hui le marché des smartphones, tablettes et objets connectés grâce à son équilibre entre performance et faible consommation.

Processeur à jeu d\'instructions réduit – processeur risc

Par ailleurs, la simplicité de RISC facilite l’implémentation dans les FPGA et ASIC, favorisant la personnalisation dans les domaines de l’embarqué et du calcul haute performance.

Pour approfondir, vous pourriez explorer comment les architectures RISC-V apportent une flexibilité inédite dans le design processeur moderne, un sujet qui ouvre de nouvelles perspectives passionnantes.