PCI Express (PCIe) – Interconnexion de composants en série

Aujourd’hui on va voir comment fonctionne PCI Express, une technologie clé d’interconnexion en série utilisée massivement dans l’informatique moderne pour relier processeurs, cartes graphiques, SSD et autres périphériques.

Introduction à PCI Express

PCI Express, ou PCIe, est un standard d’interconnexion haute vitesse fondé sur une architecture série point à point. Contrairement aux anciens bus parallèles, PCIe permet une communication bidirectionnelle simultanée entre composants via des liens série composés de plusieurs paires différentielles. Cette structure améliore la bande passante, réduit les interférences et simplifie la conception matérielle.

Architecture et topologie

PCIe organise les composants en une topologie en étoile où un commutateur (switch) ou un root complex (généralement intégré au processeur) connecte directement chaque périphérique via des lanes (voies). Chaque lane est constituée de deux paires différentielles, une pour l’envoi, une pour la réception, assurant un flux full duplex.

- Un lien PCIe est scalable : il peut comporter 1, 2, 4, 8, 16 ou 32 lanes (x1, x2, x4, x8, x16, x32).

- Chaque lane transmet des données à des débits variant selon la génération PCIe (par exemple, 8 GT/s par lane en PCIe 3.0).

- Les données circulent en série, ce qui réduit considérablement les problèmes liés à la synchronisation par rapport aux bus parallèles.

Fonctionnement en série : avantages et détails techniques

Le choix de l’interconnexion série dans PCIe offre plusieurs bénéfices :

- Réduction des interférences électromagnétiques : Les paires différentielles minimisent le bruit et les perturbations.

- Augmentation du débit effectif : En multiplexant les données sur plusieurs lanes, la bande passante totale est scalable.

- Simplicité de routage PCB : Le câblage différentiel en série est plus simple à gérer sur carte, réduisant la complexité et les coûts.

- Flexibilité : Les périphériques peuvent négocier dynamiquement le nombre de lanes utilisées en fonction des besoins.

Chaque lien PCIe utilise un protocole d’encapsulation des données, avec des paquets organisés en Transaction Layer Packets (TLP) pour le transfert entre couches. Le protocole assure la correction d’erreurs, la séquence et le contrôle de flux.

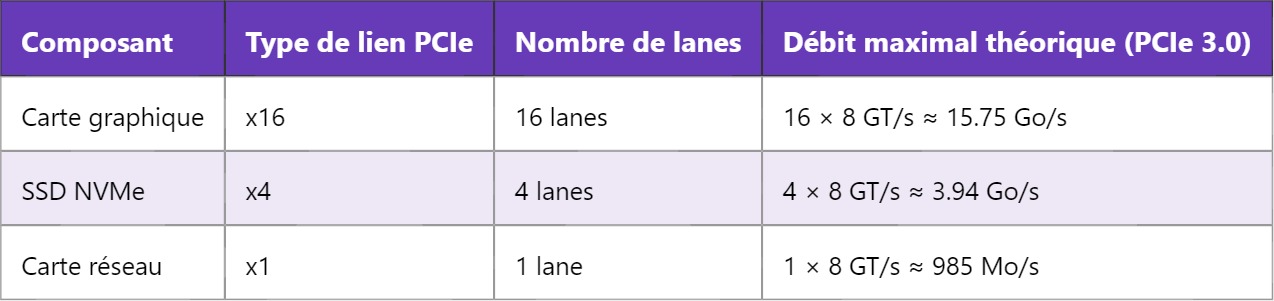

Exemple pratique d’une configuration PCIe

Cette modularité permet aux concepteurs de systèmes de choisir le bon compromis entre coût, consommation, et performance.

Points complémentaires : gestion des erreurs et évolutions

PCIe intègre des mécanismes robustes de détection et correction d’erreurs (CRC, retransmission automatique), ainsi qu’un protocole d’enchâssement pour optimiser la latence. Les différentes générations (de PCIe 1.x à 5.x et au-delà) ont multiplié le débit par lane tout en conservant la même architecture série, ce qui prouve l’efficacité de ce choix technique.

Enfin, PCIe est compatible avec la technologie Hot Plug permettant le branchement/débranchement à chaud, et supporte des fonctionnalités avancées comme la gestion d’énergie dynamique et la virtualisation.

Pour aller plus loin, découvrez comment USB4 exploite aussi le PCIe pour combiner performance et polyvalence dans un seul connecteur.