CPLD : Comprendre le Circuit Logique Programmable Complexe

Aujourd’hui on va voir en détail ce qu’est un CPLD, un composant clé dans le monde des circuits logiques programmables, qui allie flexibilité et simplicité d’usage.

Qu’est-ce qu’un CPLD ?

Le CPLD, ou Circuit Logique Programmable Complexe, est un dispositif électronique programmable utilisé pour implémenter des fonctions logiques numériques. Il se situe entre les PLD simples (Programmable Logic Devices) et les FPGA (Field-Programmable Gate Arrays) en termes de complexité et de capacité. Conçu pour offrir une logique programmable non volatile, le CPLD permet de configurer des circuits logiques selon les besoins spécifiques d’un projet.

Architecture et fonctionnement

Un CPLD est composé de plusieurs blocs logiques programmables interconnectés par un réseau de routage configurable. Chaque bloc logique contient des macrocells, qui sont des éléments pouvant réaliser des fonctions logiques combinatoires et séquentielles, comme des bascules ou des multiplexeurs.

- Blocs logiques programmables : Ces blocs contiennent des macrocells capables d’exécuter des fonctions logiques définies par l’utilisateur.

- Réseau d’interconnexion : Permet de relier les différents blocs logiques entre eux, ainsi que les entrées/sorties du CPLD.

- Bloc d’entrée/sortie : Gère les signaux d’entrée et sortie, souvent configurable pour supporter différents standards électriques.

La mémoire de configuration du CPLD est généralement non volatile (EEPROM ou flash), ce qui signifie que le circuit conserve sa programmation même hors alimentation, un avantage notable comparé aux FPGA classiques qui requièrent un chargement à chaque mise sous tension.

Avantages du CPLD

- Non-volatilité : Pas besoin de reconfiguration à chaque démarrage.

- Simplicité de conception : Architecture plus simple que les FPGA, facilitant la programmation et la débogage.

- Temps de latence faible : Les signaux logiques passent souvent par des chemins plus courts.

- Intégration aisée : Souvent utilisés pour des fonctions de contrôle ou d’interface dans des systèmes embarqués.

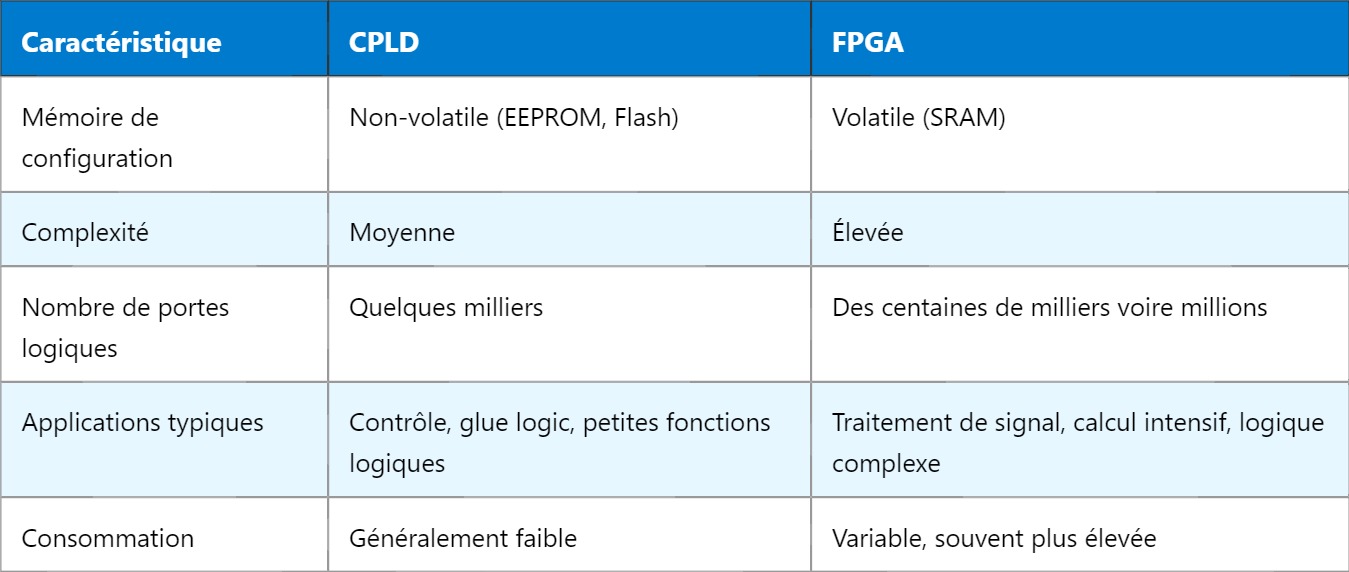

Comparaison rapide entre CPLD et FPGA

Exemple d’utilisation d’un CPLD

Supposons que vous deviez interfacer plusieurs composants numériques avec différents protocoles et signaux de contrôle dans un système embarqué. Un CPLD peut être programmé pour gérer les conversions de niveau logique, la génération de signaux d’horloge, ou encore le multiplexage de données. Sa capacité à conserver la configuration sans alimentation simplifie la maintenance et le déploiement du système.

Programmation et développement

La programmation des CPLD se fait généralement via des langages de description matérielle comme VHDL ou Verilog. Le développement passe par :

- La rédaction du code décrivant la logique souhaitée.

- La synthèse, qui transforme le code en réseau de portes logiques.

- La place et routage, qui organise les connexions internes dans le CPLD.

- La génération du fichier de configuration à téléverser dans le circuit.

Des environnements de développement intégrés (IDE) spécifiques aux fabricants, comme ceux de Xilinx (CoolRunner) ou Intel/Altera, permettent de gérer facilement ces étapes et de simuler le comportement avant programmation physique.

Cpld (composant programmable, composant logique programmable)

En résumé, le CPLD est un excellent compromis pour des applications nécessitant un contrôle logique programmable simple à moyen, avec une robustesse et une persistance de la configuration appréciables.

Pour découvrir comment les FPGA révolutionnent la logique programmable avec encore plus de puissance et flexibilité, n’hésitez pas à explorer notre article dédié aux FPGA.